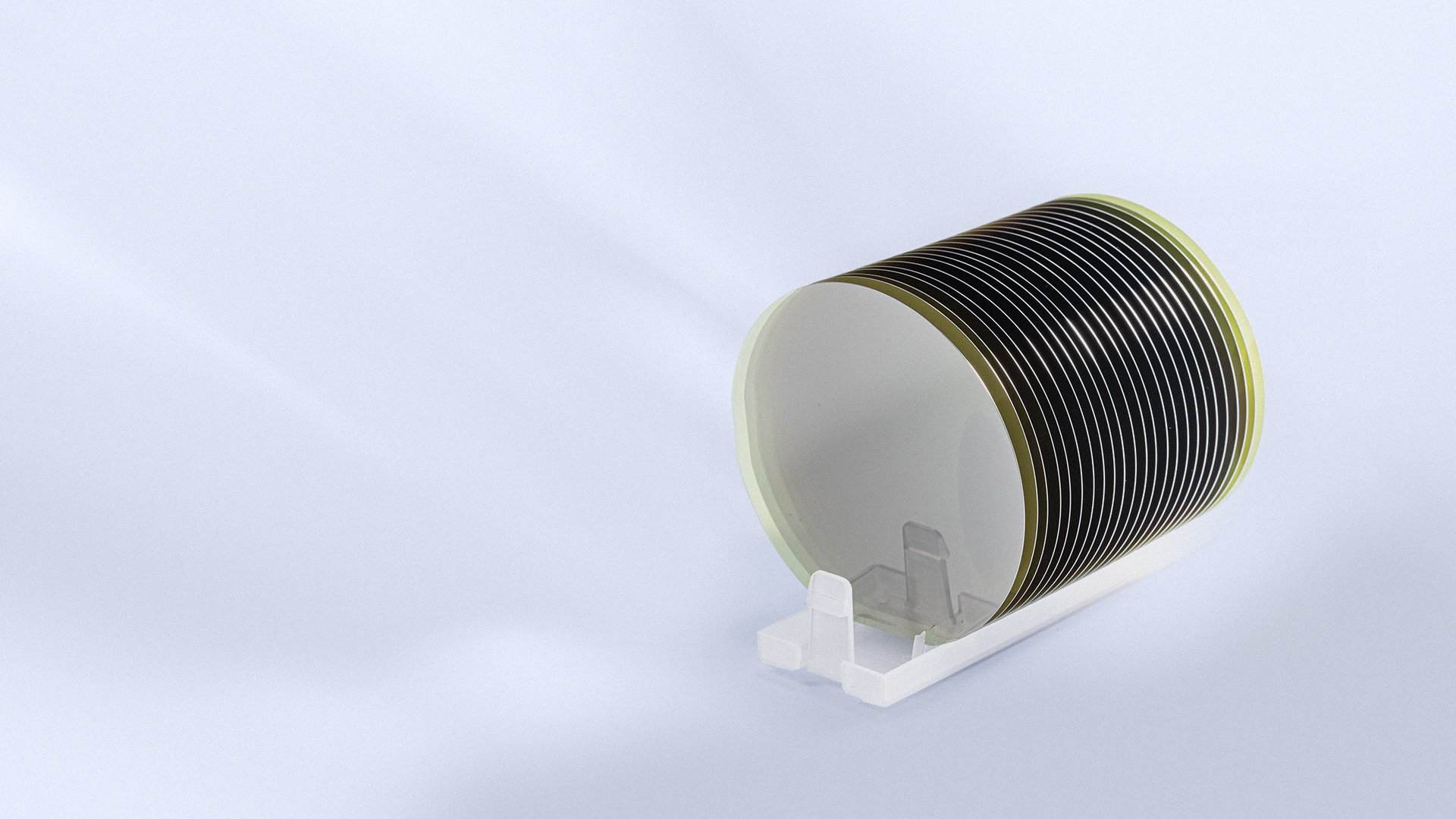

導電型炭化ケイ素基板は、導電型炭化ケイ素の結晶を切断、研削、研磨、洗浄等の工程を経て加工した単結晶シートです。単結晶基板ウェハーは、第3世代半導体の重要な原材料であり、ホモエピタキシャル成長、ウェハー製造、パッケージングテストなどのプロセスを経て炭化ケイ素ベースのパワーデバイスを製造することができ、第3世代半導体産業の発展にとって重要な基礎材料となっています。また、多様化するお客様の小型製品ニーズに応えるため、4インチ以下の小型製品の生産能力を一部残し、安心して供給できる体制を整えています。

炭化ケイ素基板材料は、ホモエピタキシャル成長、ウェハー製造、パッケージングテストおよびその他のプロセスを経て、炭化ケイ素ダイオード、炭化ケイ素MOSFETおよびその他のパワーデバイスを製造します。高温、高電圧、大電流およびその他の動作環境に適しており、新エネルギー自動車、充電パイル、太陽光発電・風力発電、エネルギー貯蔵、軌道交通、スマートグリッド、産業用電源、産業用駆動装置、白物家電などの分野で広く応用されています。

| Diameter | 99.5 mm - 100.0 mm | |

| Poly-type | 4H | |

| Thickness | 350 μm ± 15 μm | |

| Wafer Orientation | Offaxis : 4.0°toward < 11-20 > ± 0.5° | |

| Micropipe | ≤ 0.2 cm-2 | |

| Resistivity | 0.015-0.024 Ω·cm | |

| Primary Flat Orientation | {10-10} ± 5.0° | |

| Primary Flat Length | 32.5 mm ± 2.0 mm | |

| Secondary Flat Length | 18.0 mm ± 2.0 mm | |

| Secondary Flat Orientation | Silicon face up: 90° CW. from Prime flat± 5.0° | |

| Edge Exclusion | 3 mm | |

| LTV / TTV / Bow / Warp | ≤2.5 μm/ ≤ 5 μm/ ≤ 15 μm/ ≤ 30 μm | |

| Roughness | Polish Ra ≤ 1 nm | |

| CMP Ra ≤ 0.2 nm | ||

| Edge Cracks By High Intensity Light | - | |

| Hex Plates By High Intensity Light | Cumulative area ≤ 0.05% | |

| Polytype Areas By High Intensity Light | - | |

| Visual Carbon Inclusions | Cumulative area ≤ 0.05% | |

| Silicon Surface Scratches By High Intensity Light | - | |

| Edge Chips High By Intensity Light | None permitted ≥ 0.2 mm width and depth | |

| Silicon Surface Contamination By High Intensity | - | |

| Threading Screw Dislocation | ≤ 500cm-2 | |

| Packaging | Multi-wafer Cassette Or Single Wafer Container | |

| Diameter | 99.5 mm - 100.0 mm | |

| Poly-type | 4H | |

| Thickness | 350 μm ± 25 μm | |

| Wafer Orientation | Offaxis : 4.0°toward < 11-20 > ± 0.5° | |

| Micropipe | ≤ 15 cm-2 | |

| Resistivity | 0.015 -0.028 Ω·cm | |

| Primary Flat Orientation | {10-10} ± 5.0° | |

| Primary Flat Length | 32.5 mm ± 2.0 mm | |

| Secondary Flat Length | 18.0 mm ± 2.0 mm | |

| Secondary Flat Orientation | Silicon face up: 90° CW. from Prime flat± 5.0° | |

| Edge Exclusion | 3 mm | |

| LTV / TTV / Bow / Warp | ≤ 10 μm/ ≤ 15 μm/ ≤ 25 μm/ ≤ 40 μm | |

| Roughness | Polish Ra ≤ 1 nm | |

| CMP Ra ≤ 0.5 nm | ||

| Edge Cracks By High Intensity Light |

Cumulative length ≤ 10 mm Single length ≤ 2 mm |

|

| Hex Plates By High Intensity Light | Cumulative area ≤ 0.1% | |

| Polytype Areas By High Intensity Light | Cumulative area ≤ 3% | |

| Visual Carbon Inclusions | Cumulative area ≤ 3% | |

| Silicon Surface Scratches By High Intensity Light | Cumulative length ≤1 × wafer diameter | |

| Edge Chips High By Intensity Light | 5 allowed, ≤ 1 mm each | |

| Silicon Surface Contamination By High Intensity | - | |

| Threading Screw Dislocation | - | |

| Packaging | Multi-wafer Cassette Or Single Wafer Container | |

-

4 Inch Conductive SiC Substrate Specification.pdf今すぐダウンロード